Dual Core (DSP and MCU) - Industrial Control Applications The SH99F100 is a dual-core (DSP and MCU) chip for industrial control applications such as motor speed regulation and variable frequency power supplies. The MCU can be used to handle switching, input and output, and communication, while the DSP only needs to focus on the operation of the control algorithm. The DSP architecture consists of three parallel computing units (ALU, MAC, SHIFTER), two independent address generators (DAGs), and a powerful program sequencer (PSQ). The calculation unit provides the computational functions that all processors can provide, including single-cycle multiply/accumulate, bit operations, shift operations, and more. The dual data address generator allows the processor to simultaneously fetch two data from two data banks (Data Memory and Program Memory) in one cycle. The program sequencer implements single-cycle operation of all instructions, fast interrupt response, and nested cycles of non-CPU intervention. The 16-bit PWM module, Quadrature Coding Interface (QEI) and 14-bit pipelined ADC and op amp (OP) act as internal peripherals for the DSP core, enabling easy implementation of multiple industrial control algorithms. The MCU core is a high-speed and high-efficiency 8051-compatible core. Compared with the traditional 8051 chip, the MCU core has faster running performance and superior performance. Its resources include built-in 256-byte SRAM and external 3840-byte SRAM. Three 16-bit timers and three external interrupts, as well as two enhanced UARTs and one SPI interface. Dual-core architecture: 16-bit enhanced DSP + 8-bit MCU DSP and its peripherals:

â–²CPU - Maximum 100MIPS, 16-bit wide data bus - Single-cycle synchronous execution of 16-bit MAC and access operations - 32-stage barrel shifter - Single-cycle execution "take double operands" and "fetch instructions"

â–² On-chip memory - 64K X 8bits Flash as DSP's non-volatile memory - 16K X 24bits SRAM as DSP running program Code Memory - 6K X 16bits SRAM as DSP Data Memory - 512 X 16bits SRAM as communication data memory (located in DM Area) - 2K X 16bits SRAM as DSP Program Memory (located in PM area)

â–² Pulse Width Modulation (PWM) Module - 6 (3 pairs) 16-bit PWM output - 3 time base counting modes: single event mode, edge-aligned mode and center-aligned mode - 2 output modes per pair of PWM: complementary output And independent output - PWM output effective polarity selection

Deadband Generation Logic - Auto Update Cycle, Duty Cycle, Output Polarity, and ADC Trigger Time - 5 Protection Input Pins - Debounce Time on each Protection Input Pin Can Be Set to Eight (0ms - 16ms) - After Frequency division coefficient

â–² Quadrature Encoder Interface (QEI) - QEA, QEB, Index three-way signal input - 16-bit up/down bidirectional position counter - 5 kinds of maskable interrupts: counter reload / Index signal interrupt; Index signal error interrupt; QEA /B input signal phase error interrupt; tachometer timer overflow interrupt; tachometer timer capture interrupt

â–² 2 X 8-channel 14-bit analog-to-digital converter (ADC) - 10MSPS slew rate - two simultaneous parallel sampling modes, two independent sequential sampling modes and single sequence sequential sampling mode

â–² 4 16-bit timers DTImer0/1/2/3

â–² 3 external interrupts DXINT0/1/2

â–²1 JTAG interface for DSP simulation debugging

â–² 4 input capture function pins - use one of DTImer2/3 as time base - 2 level FIFO buffer - capture event can be set to rising edge, falling edge, rising/falling edge - input frequency dividing / filtering setting

â–² 3 output compare pins - use one of DTImer3/2 as time base - single compare mode, double compare mode, edge-aligned PWM output mode

â–² 2 operational amplifier MCUs and their peripherals:

â–²CPU - 8-bit microcontroller based on 8051 instruction pipeline structure - maximum operating frequency 16MHz, CISC instruction set

â–² On-chip memory - 64KBytes Flash - 4KBytes SRAM - 1K X 8bits Flash as ISP program memory

â–² 56 CMOS bidirectional I/O pins (functional multiplexing), built-in input pull-up resistor

â–²SPI interface (master/slave mode)

â–² 2 enhanced UARTs

â–² 3 16-bit timers TImer0/1/2

â–² 3 external interrupts INT0/1/2

â–² 8-channel 10-bit successive approximation analog-to-digital converter (ADC)

â–² 3-channel 12-bit pulse width modulation (PWM) output 1 JTAG interface for MCU simulation debugging

â–² working voltage: VDD = 2.7 - 5.5V

â–² Stop vibration detection - Switch to internal RC as system frequency and generate interrupt after external crystal failure

â–² ISP function

â–² watchdog timer (WDT)

â–² low voltage reset LVR

â–²Package: LQFP100

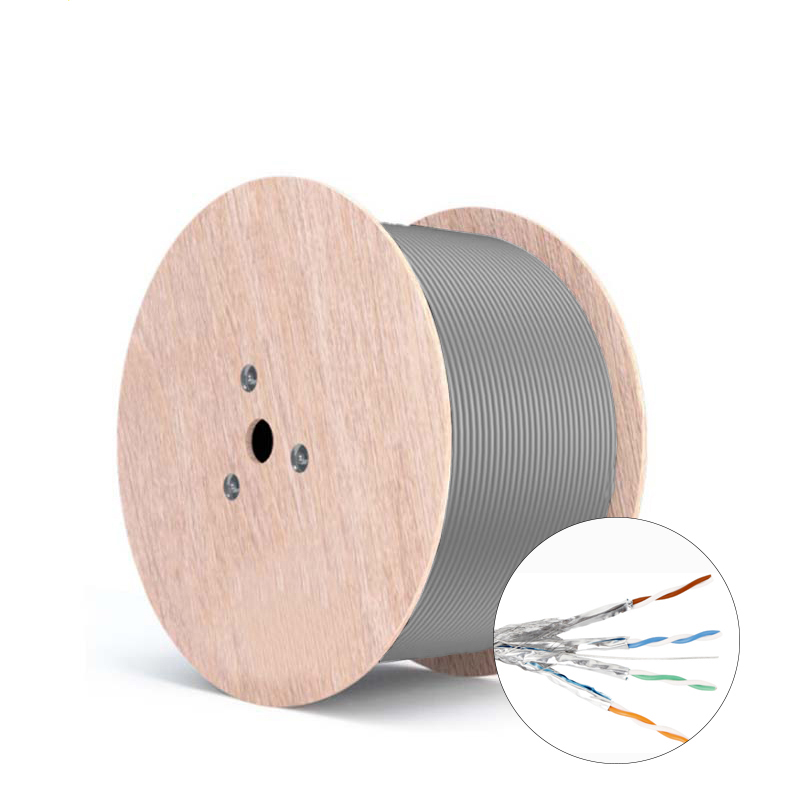

The cat7 Lan Cable are an eight-core Shield wire. Each pair has a Shield layer (commonly called a Foil Shield), and then a Shield layer (commonly called a Braided screen Shield) outside the eight cores, with the same connection as the RJ-45.The highest transmission frequency of the CAT7 Ethernet Cable S/FTP is 600MHz, and the transmission frequency of the CAT7 Network Cable is 1000MHz.

There are a number of significant differences between the six and seven cabling systems, the most obvious of which is bandwidth.The CAT6 cable of channels provide a comprehensive attenuation to crosspoint ratio of at least 200MHZ and an overall bandwidth of 250MHZ. CAT7 of systems can provide at least 500MHZ of comprehensive attenuation to crosspoking ratio and 600MHZ of overall bandwidth.

The proliferation of broadband applications has created a need for more bandwidth.For example, a typical CAT7 channel can provide a bandwidth of 862MHZ for the transmission of video signals, analog audio signals on another pair, and high-speed LAN information on a third or fourth pair.

Another difference between the CAT6 patch cable and cat7 patch cable systems is their structure.The six types of wiring systems can use either UTP or STP.The seven types of systems are based only on shielded cables.In the cat7 network cables, each pair has a shield layer, and four pairs of wires together have a common shield layer.In terms of physical structure, the additional shielding layer makes the CAT7 Ethernet Cable have a larger diameter.

Another important difference is its ability to connect hardware. The parameters of the cat7 patch cable of systems require that all pairs of wires provide at least 60DB of integrated proximal winding at 600MHZ.The cat6 systems only require 43dB at 100MHZ and 46dB at 250MHZ for the cat6 patch cable.

Cat 7 Ethernet Cord,Cat7 Lan Cable,Cat 7 Ethernet Cable,Cat 7 Network Card

Shenzhen Kingwire Electronics Co., Ltd. , https://www.kingwires.com